2 硬件电路设计

2.1 CY7C68013结构和功能说明

2.1.1 CY7C68013内部结构

CY7C68013型单片机是赛普拉斯公司生产的高速外部处理器,也是EZ-USB FX2TM USB微处理器[5]。

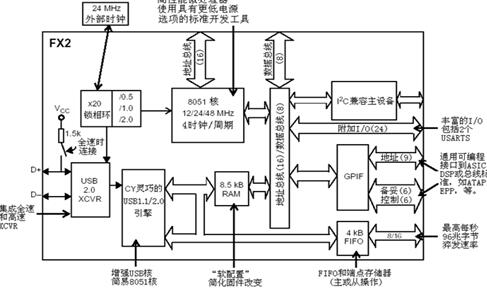

如图2.1所示,CY7C68013的内部主要包括增强的8051微控制器,USB 2.0收发器,SIE(串行接口引擎)以及可编程成的外部接口。主/从端点FIFO和GPIF(通用可编程接口),可以实现数据传输和程序下载等功能,让用户可以快速地编写程序并投入市场,加快了产品从设计到上市的速度。此外,他的核心部件含有独特的FX2体系结构,包含USB2.0的串行接口引擎,这使数据传输速率可以达到USB 2.0允许的最大带宽——56Mbytes/s,保证了数据传输的速度[6]。

图2.1 CY7C68013框图

2.1.2 CY7C68013的管脚分配

图2.2显示的是CY7C68013的管脚图,它包含了128个引脚和40个I/O口。AVCC是模拟 VCC,它为芯片的模拟部分供电,使用时需要让此引脚与 3.3V 电源连接。AGND与其类似,代表模拟接地,需要将他与地线用尽可能短的线连接。DMINUS和DPLUS分别与USB的D+和D-信号相连,实现单片机和USB接口的连接。A0-A15

是8051的 地址总线,它们始终处于驱动状态。当 8051 处理内部 RAM 时,A0-A15反映内部地址。D0-D7是8051 数据总线。该双向总线在处于非活动状态、读总线输入和写总线输出时具有高阻抗。数据总线用于外部 8051 程序和数据存储器。数据总线在挂起时总是处于低电平驱动状态,它仅在访问外部总线时处于活动状态。

此外,在芯片上数目最多的管脚是类似于PA0-PA7这样的多路复用引脚,它们不仅可以实现一种功能,而是可以根据标志位的不同而实现两种功能。比如PA0/INT#口,其功能通过 PORTACFG.0 来选择。当选用PA0功能时,它是双向 I/O 端口引脚。当使用INT0#功能时,它是低电平有效的8051 INT0 中断输入信号,可边沿触发 (IT0 = 1) 或电平触发 (IT0 = 0)。 射频模块的CY7C68013单片机电路和程序设计(3):http://www.youerw.com/tongxin/lunwen_15909.html