由以上分析可知,三种频率合成技术各有优点,然而没有一种方式可以满足技术上的所有要求,即没有一种合成技术可以同时满足小体积、低噪声、高频率分辨率、宽带宽、高转换速率、低功耗等指标,所以在选择频率合成方案的需要根据实际需要综合考虑。

2.2 DDS结构与基本原理

2.2.1 DDS结构

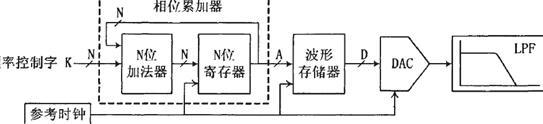

DDS电路一般由参考时钟(CLK)、相位累加器(Adder)、波形存储器(ROM)、D/A转换器(DAC)和低通滤波器(LPF)组成[9]。其结构如图2.1所示。

图2.1 DDS基本结构框图

图2.1中N为相位累加器位数,N位相位累加器由N位加法器和N位寄存器组成,K为频率控制字,A为波形存储器地址位数,D为DAC转换器位数, 为输出频率。

相位累加器由一个N位加法器和一个N位寄存器级联组成,用来实现相位累加功能,即将寄存器中前一个相位值与当前系统的频率控制字相加得到下个相位值。整个2π周期的相位被一个N位字长的累加器分成 个离散的相位,其最小相位增量为2π/ 。在参考时钟(CLK)的上升沿到来时,相位累加器累加输入的频率控制字,假设相位累加器位数N=3,则可以输出对应八种状态的二进制相位序列码,即000-111。此处,将000状态对应的相位表示为π/8,那么存储器的地址所对应的相位值如表2.1所示。

表2.1 存储器地址对应的相位值

用频率控制字表示相位增量,

当K=1,N=3时,相位增量为2π/8,此时输出信号频率 ;

当K=2,N=3时,相位增量为4π/8,此时输出信号频率 ;

当N=3时,DDS的频率分辨率为 ,理论上能够输出4个频率。系统频率分辨率同时受系统时钟频率大小及相位累加器位数两个因素影响。

波形存储器(ROM)的作用是存储包含所需产生波形信号一个周期的幅度信息,波形存储器的地址是对应的相位二进制序列码与累加器高A位相连,每一个地址对应波形相应的幅度值[10]。查表时,用相位累加器的高A位对波形存储器进行寻址,波形ROM地址数代表了存储器ROM的存储容量及存储波形幅度值的点数,如32位相位累加器的高8位作为波形ROM的寻址码,则波形ROM的容量为 =256。寻址后波形存储器ROM输出该地址对应的二进制幅度序列码。

我们一般把能将数字信号转换成模拟信号的电路成为D/A转换器[11]。数字信号输入量是N位二进制编码信号,模拟信号输出量是以电流或电压形式提供,整个转换过程就是个二进制数转换为十进制数的过程。要实现数字量到模拟量的转换,必须将以二进制代码表示的数字输入量按照每一位的权值产生相应大小的模拟量最终将每一路模拟量相加,便可得到与数字信号输入量对应的总模拟信号输出量。一个完整的D/A转换器原理图应包含参考电压、比例网络、二进制开关及输出放大器。在实际应用中,为了实现D/A转换器与其他电路的接口,往往还需要在输入端增加数据锁存器来保存从外电路输入进来的数据,在输出端则需要增加采样保持电路以便转换后的数据能够正确被外电路读走。D/A转换器在电路系统中拥有广泛的应用,根据其工作原理可分为电流定标电路、电压定标电路和电荷定标电路。

D/A转换器输出的信号波形是阶梯波。为了最终能够得到平滑的波形曲线,需要在D/A转换器之后连接一个模拟低通滤波器(LPF)以滤去主频附近的非谐波分量。

图2.2为DDS各个部分的输出信号。

图2.2 DDS各部分输出波形

DDS系统采用高稳定信号源作为时钟信号,随着时钟的到来累加器寄存器会不断将上一个累加值与当前频率控制字进行累加。由于加法器位数有限,累加器会产生溢出即此时完成对波形存储器中数据一整个循环的寻址过程,相应在系统输出端输出了一个周期的波形。溢出的频率随频率控制字K的增大而增大,代表了所要合成信号的频率大小。为了方便,在控制系统时钟频率不变的情况下,通过改变频率控制字的大小来改变数输出频率。DDS系统的频率控制字采用二进制表示,实际中为使用方便会通过数学运算将从外界输入的十进制频率值转换为二进制频率控制字。图2.3和图2.4分别为DDS相位累加器和波形ROM的示意图。 FPGA控制DDS的频率发生器设计(4):http://www.youerw.com/tongxin/lunwen_21740.html