2 C6000系列DSP自加载的方式及原理

DSP的处理系统在成品化了以后,需要脱离仿真器独立运行。当今科技的飞速发展,使得高速DSP内存不再是基于低速的flash结构,而是基于高速的RAM结构[11]。目前高性能DSP大多数基于高速RAM结构,系统在断电后内部RAM上的数据与程序会全部丢失。因此,DSP在上电时必须通过某种方式将存储在外部非易失性存储器中的用户代码复制到片内缓存RAM或片外同步动态随机存储器(Synchronous Dynamic Random Access Memory ,SDRAM)中去自动运行,以完成DSP程序的加载和系统启动,此过程称为DSP的自加载。

2.1 C6000系列单核DSP自加载原理

C6000系列的DSP有三种启动配置:无引导,ROM引导,主机引导。引导模式是由boot mode管脚决定的。最常见的启动配置是ROM引导。

Flash或ROM是非易失性存储器,存储在里面的数据在断电后也不会丢失。嵌入式产品的数据与程序一般都放在这两种存储器中[12]。ROM boot DSP的模式下,C621x/C671x/C64x系列的DSP 增强型直接内存存取(Enhanced Direct Memory Access,EDMA)接口都直接自动地从CE1存储器映射空间复制1K 代码到内部RAM的地址0。在这个过程中,中央处理器(Central Processing Unit,CPU)停止运行,搬移完成后,CPU才从地址0开始运行[13]。

本节以C6455为例来介绍ROM加载原理。C6455地址空间0x100000到0x107FFF集成了32K的内部ROM。在这部分ROM中,固化了部分被称为“bootloader”的引导代码[14]。DSP内部用于实现模式选择和程序读取功能的部件就是Bootloader。由于其本身的限制,读取代码的长度有限,在用户程序较大时,需要进行二次引导。首先DSP的用户程序放在外部flash中,其次当系统上电后,DSP通过EMIF接口访问外部flash,并将flash 地址空间0xB0000000到0xB00003FF的1KB内容搬移到二级静态随机存储器(L2 Static RAM,L2 SRAM)地址空间0x00800000 到0x008003FF内存上,最后当搬移完成之后,DSP将会从0x00800000开始运行程序。在上电之前需要将拨码开关拨到相应位置进行模式选择[15]。

如果用户程序的机器代码长度小于1KB,我们便可以将此用户代码烧写进flash的前1KB内存中[16]。若DSP复位,EDMA就会自动将程序加载到内存SRAM,并在加载完后执行此程序。此读取flash的过程完全是自动完成的,不需要CPU的参与,此过程称为一级加载。

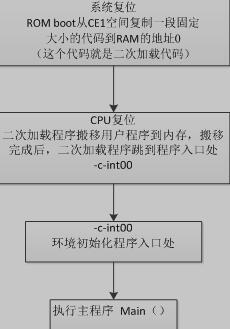

若用户程序的机器代码长度大于1KB时,假定此用户程序长度为M,M大于1KB,已经被烧写到了flash的内存空间里面,并且这个内存空间不占用CE1的前1KB的地址[17]。这样我们就可以编写一小段汇编语言程序,放在CE1的前1KB空间内,此段程序主要作用是将放置在flash中的用户代码加载到内存RAM中去,搬移完后跳转到C语言的环境初始化程序的入口处-c-int00,然后再执行主程序,这样整个搬移以及启动过程就完成了,这个1KB的代码称为二次加载程序。这段代码搬移用户程序的过程称为二次加载过程[18]。此过程可以用图2.1表示[19]。

图2.1 C6455 flash二次加载流程图

2.2 C6000系列多核DSP自加载

2.2.1 TMS320C6678 DSP的自加载原理

本节以C6678为例来介绍多核DSP的自加载原理。在TMS320C6678的地址空间0x20B00000到0x20B1FFFF间集成了128K的内部ROM[20]。此段ROM中固化了一段称为“bootloader”的引导代码,其主要功能有两点:其一是在系统上电时,对C6678进行一些必要的配置,用来辅助EMIF/PCI/SPI等接口进行加载;其二是将代码从外部存储器搬移到内部L2 SRAM,以完成代码加载。

TMS320C6678有8个核,但bootloader 只有一份,故8个核都执行bootloader的代码,bootloader会根据核号(DNUM)进行不同的功能处理。就core0而言,它主要用来读取DEVSTAT 寄存器的值,并根据当前加载模式初始化接口并设置PLL,判断加载模式来确定是否需要进行搬移数据。就其它的7个核而言,它们主要作用是挂载IPC中断,再进入IDLE状态等待core0发中断,中断来了,马上就跳至入口地址处执行程序[21]。各核的bootloader执行过程如图2.2所示。 基于C6000系列DSP BOOT的研究与实现(3):http://www.youerw.com/tongxin/lunwen_23265.html